# **Operational Amplifiers**

Tuesday, January 4, 2022 3:43 PM

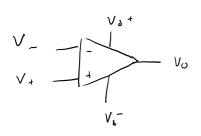

Det Op Amps are general purpose voltage amplifiers

and: Vs - < Vo < Vs+

$$V_o = A (V_4 - V_-) = A V d$$

where A is the open loop voltage gain

Def

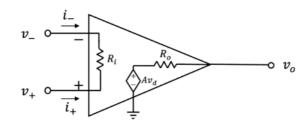

# Linear model

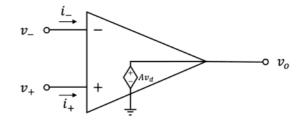

# **Ideal model**

Tuesday, January 4, 2022 3:51 PM

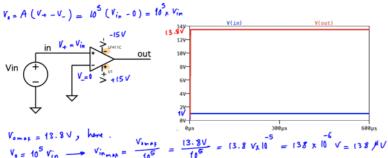

Open-loop operation of op-amps (no feedback)

In open-loop configuration, op-amp cannot amplify input voltages greater than a few micro volts. It cannot be used as a voltage amplifier.

Voman = 13.8 V and A = 10 5

Thus it is not an effective amplifier

Det Feedback: portion of output is

that the output signal would reach the desired stable level.

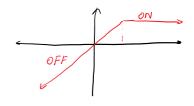

Positive feedback: In circuits with positive feedback, when the Negative feedback: In circuits with negative feedback, as the output increases, the input will also increase, and vice versa. output increases, the input will decrease, and vice versa, such The output of circuits with positive feedback is always at its limits.

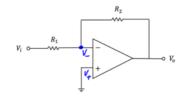

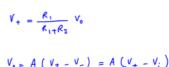

$$V_{-} = \frac{R_2}{R_1 + R_2} V_0^{-} + \frac{R_1}{R_1 + R_2} V_0$$

In General:

$$\frac{V_0}{V_1} = -\frac{R_2}{R_1}$$

.  $\frac{1}{1+\frac{1}{4R}}$

$$B = \frac{R_1}{R_1 - R_2}$$

$B = \frac{R_1}{R_2 - R_2}$

Victual Short Principle: Vo is afinite value

$$V_o = A v_d - v_d = \frac{V_o}{A} \approx 0$$

then:

$$\frac{V_0}{V_i} = -\frac{R_1}{R_2}$$

## Limitations

Thursday, January 6, 2022 5:26 PM

Saturation: since  $V_s^- \leq V_o \leq V_s^+$ , the output is limited by the power supply voltage.

Current: op-amps have a maximum output current.

# Semiconductors (P-type, N-type)

Sunday, January 9, 2022 4:29 PM

N-type semiconductors: doped with group S elements - has extra electron.

P-type semiconductors: doped with group 3 elements - has extra holes

both N-type and P-type are electrically neutral

In a P-N junction diade, a P-type and N-type are connected.

P-type

N-type

when (+) voltage and (-) voltage are applied to the P-type and N-type

then it is forward brased

the opposite is backward brased

Idea During forward binsing, the width of the barrier potential decreases until the whole diode conducts a current.

During reverse binsing, the width of the barrier potential widens and only some small reverse current is conducted.

barrier potential

#### Diodes

Sunday, January 9, 2022 5:27 PM

Symbol:

IV characteristic (piecewise): when diode is of:  $I_0 = 0$ ,  $V_0 < V_T$  when diode is on:  $I_0 = 0$ ,  $V_0 = V_T$

Solving: assume either the diode is off or on, and solve for Vp to either verity the assumption or reject the assumption.

Stops: 1) assume diade is off

- 2) find Vp, if Vo < V, diode is off

- 3) assume diode is on

- 4)  $V_0 = V_7$ , find  $I_0$ , if  $I_0 \ge 0$  then diode is on, otherwise off

## LEDs, Zener Diodes

Tuesday, January 11, 2022 4:36 PM

LEQ: Larger band gap,  $V_7 \approx 1.7V - 1.9V$

-5

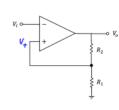

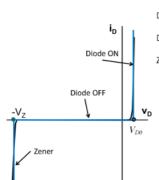

Zener Diode: Typical diode IV for forward bias, when  $V_0 \ge V_T$ ,  $V_0 = V_T$ ,  $I_0 \ge 0$ Allows current to flow in reverse bias in reverse direction

IV characteristic:

Diode ON:  $v_D = V_{D0}$  and  $i_D \ge 0$

Diode OFF:  $i_D = 0$  and  $-V_Z < v_D < V_{D0}$

Zener:  $v_D = -V_Z$  and  $i_D \le 0$

Symbol: -

$ON: V_D = V_T, I_D \ge 0$

OFF: Vz < Vo < VT, I = 0

Zener: Vo = -V2, In = 0

# Diode Waveform Shaping Circuits

Thursday, January 13, 2022 7:31 PM

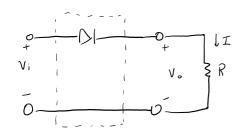

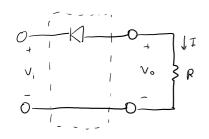

1) Rectifier Circuits:

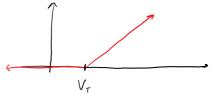

when  $V: \langle V_T, V_0 = 0$ when  $V_i \ge V_T, V_0 = V_i - V_T$

when  $V_1 > V_T$ ,  $V_0 = 0$ when  $V_2 \leq V_T$ ,  $V_0 = V_1 + V_T$

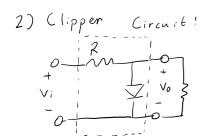

when  $V_i \leq V_T$ ,  $V_0 = V_i$ when  $V_i \geq V_T$ ,  $V_0 = V_T$

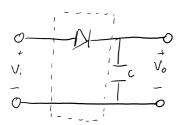

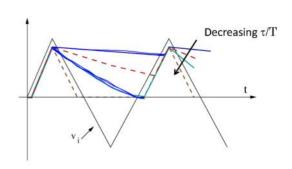

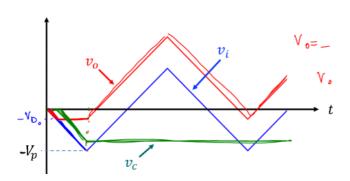

3) Peak Detector Circuito:

when  $V_i \in V_C + V_T$ ,  $V_D \in V_T$ ,  $I_D = 0$  and  $V_O = V_C$  when  $V_i \stackrel{>}{=} V_{C-1} V_T$ ,  $V_D = V_T$ ,  $I_D \stackrel{>}{=} 0$  and  $V_C = V_i - V_O$  Idealy, the capacitor does not discharge, so  $V_C$  stays constant after every peak.

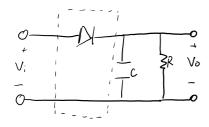

In practice, there is always a resistor in parallel:

when  $V_i < V_{C-1}V_T$ ,  $V_D < V_T$ ,  $I_D = 0$ and  $V_C = V_C e^{-(t-t_0)/2}$  where Y = RCwhen  $V_i \ge V_{c-1}V_T$ ,  $V_D = V_T$ ,  $I_D \ge 0$  and  $V_C = V_i - V_0$

Ideal case: Does not decrease over time Practical case: Decreases at rate e-lt-to>/2

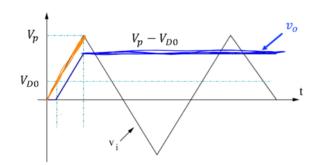

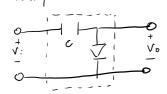

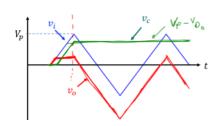

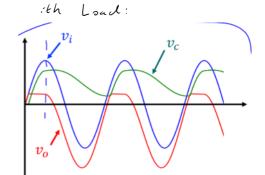

4) Clamp Circuits:

In general!  $V_0 = V_7 - (V_p - V_7)$ Always:  $V_0 = V_7 - V_6$  where  $V_6 = V_p - V_7$

Without Load:

The diode turns OFF when the capacitor is charged to  $v_c = V_p - V_{D0}$

$$v_o = v_D = v_i - v_c$$

Diode off:  $v_0 = v_i - (V_n - V_{n0})$

To solve: solve for the peak detector,  $V_0 = V_1 - V_2$

By reversing the disde and voltage source, we can shift positively:

Reverse:  $V_c$  charges to  $-(V_p - V_T)$  $V_o = V_c - V_c = V_c + (V_p - V_T)$

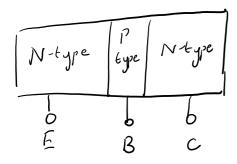

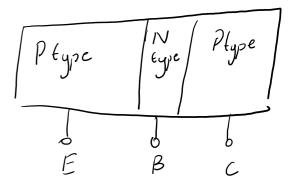

# BJT (Bipolar Junction Transistor)

Thursday, January 27, 2022 5:02 PM

NPN:

PNP:

Construction: Thin base region (between Exc)

Heavily doped emitter

· Large area collector

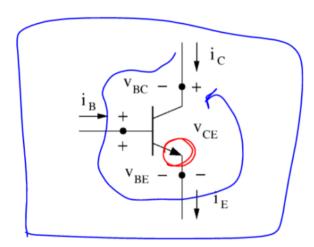

# **NPN** transistor

Circuit symbol and Convention for current directions

# KCL: $i_E = i_C + i_B$

$$\mathsf{KVL:}\ v_{BC} = v_{BE} - v_{CE}$$

Note:

$$v_{CE} = v_C - v_E$$

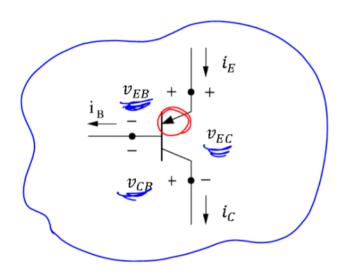

# **PNP** transistor

KCL:

$$i_E = i_C + i_B$$

KVL:

$$v_{CB} = v_{EB} - v_{EC}$$

Note:

$$v_{EC} = v_E - v_C$$

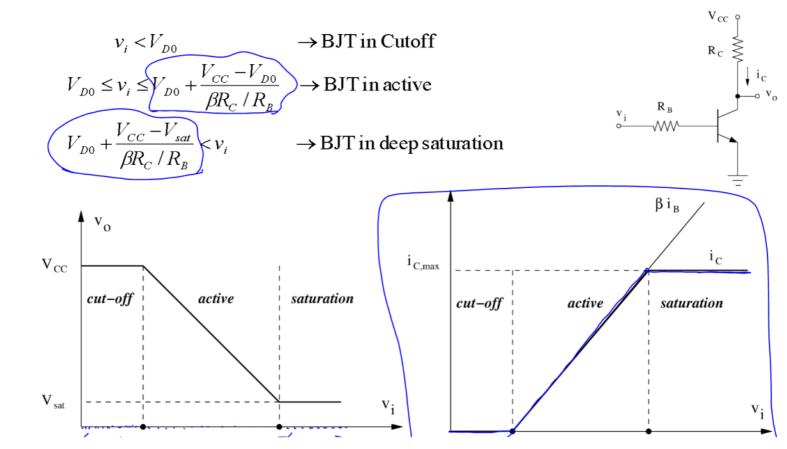

# **BJT Operation Modes**

Thursday, January 27, 2022 5:12 PM

When BJT is in out off mode:

$I_g = 0$ ,  $I_c = 0$   $I_E = 0$

When BJT is in active mode!

$I_{B} \ge 0$   $V_{BE} = V_{DO}$   $I_{C} = B \cdot I_{B}$   $V_{CE} \ge V_{DO}$

When BJT is in Suburation mode:

IB 30 VBE = VDO IC < BIB VCE = V SONE

where B is the current gain of the BJT

Note: For Si based BJT, it Voo is not given, Vpo = 0.7 V

# **BJT Transfer Functions**

Tuesday, February 1, 2022 5:35 F

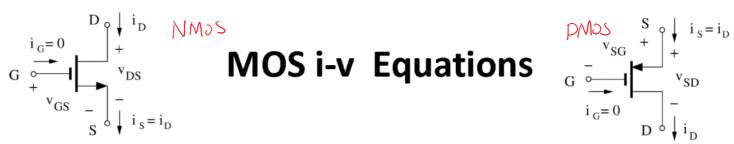

$$\begin{array}{c|c} \text{PMOS} & S & i_S = i_D \\ \hline v_{SG} & + & + \\ G & & V_{SD} \\ \hline i_G = 0 & - \\ D & & i_D \end{array}$$

NMOS (

$$V_{OV} = v_{GS} - V_{tn}$$

)

Cut- Off:

$$V_{OV} < 0$$

$i_D = 0$

Triode:

$$V_{OV} \ge 0$$

and  $v_{DS} \le V_{OV}$   $i_D = 0.5 \, \mu_n C_{ox} \frac{W}{L} (2 \, V_{OV} v_{DS} \, - v_{DS}^2)$

Saturation:

$$V_{OV} \ge 0$$

and  $v_{DS} \ge V_{OV}$   $i_D = 0.5 \, \mu_n C_{ox} \frac{W}{L} \, V_{OV}^2 \, (1 + \lambda v_{DS})$

PMOS

$$(V_{OV} = v_{SG} - |V_{tp}|)$$

Cut- Off:

$$V_{OV} < 0$$

$i_D = 0$

Triode:

$$V_{OV} \geq 0$$

and  $v_{SD} \leq V_{OV}$   $i_D = 0.5 \, \mu_p C_{ox} \frac{W}{L} (2 \, V_{OV} v_{\rm SD} \, - v_{SD}^2)$

Saturation:

$$V_{OV} \ge 0$$

and  $v_{SD} \ge V_{OV}$   $i_D = 0.5 \, \mu_p \, C_{ox} \, \frac{W}{L} \, V_{OV}^2 \, (1 + \lambda v_{SD})$

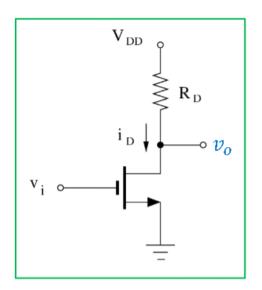

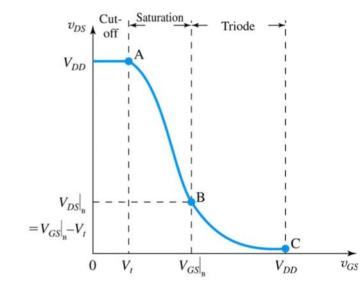

Def For the NMOS circuit:

The transfer function:

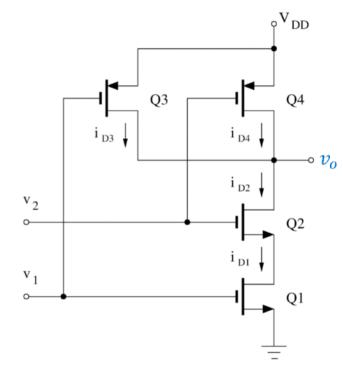

## **CMOS** Inverter

Monday, February 14, 2022 12:10 PM

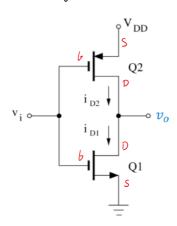

Det Replacing the resistor in the NMOS inverter with a PMOS:

where: GS1 KVL:

$$v_{GS1} = v_i$$

GS2 KVL:

$$V_{DD} = v_{SG2} + v_i$$

DS1&2 KVL:

$$V_{DD} = v_{SD2} + v_{DS1}$$

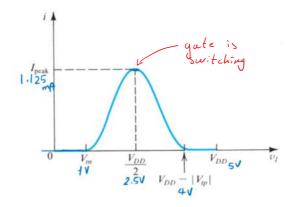

KCL:

$$i_{D1} = i_{D2}$$

$$v_o = v_{DS1} = V_{DD} - v_{SD2}$$

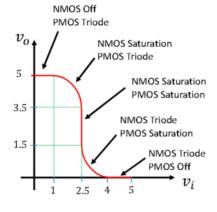

The transfer function of the inverter are: (assuming kn=kp and Vtn=V6p)

Tuesday, February 15, 2022 6:15 PM

# **Truth Table**

$$v_1 = \mathbf{0}$$

$v_2 = \mathbf{0}$

$$v_o = V_{DD}$$

$$\boldsymbol{v}_1 = \mathbf{0}$$

$$v_2 = V_{DD}$$

:

$$v_o = V_{DD}$$

$$\boldsymbol{v}_1 = \boldsymbol{V}_{DD} \quad \boldsymbol{v}_2 = \boldsymbol{0} :$$

$$v_o = V_{DD}$$

$$egin{aligned} m{v}_1 &= m{0} & m{v}_2 &= m{0}; \\ m{v}_1 &= m{0} & m{v}_2 &= m{V}_{DD}; \\ m{v}_1 &= m{V}_{DD} & m{v}_2 &= m{0}; \\ m{v}_1 &= m{V}_{DD} & m{v}_2 &= m{V}_{DD}; \end{aligned}$$

$$v_o = 0$$

when gate is 0: NMOS: off PMOS: in triple

when gate is VDD NMOS: in triode PMOS: off

# **Transistor Amplifiers**

Tuesday, February 22, 2022 5:49 PM

Det We can design a linear amplifier using BIT or MOSFETS

The transfer function: Vo must be constant and is the voltage gain

MOSFET:

When a MOSFET is in saturation, its Evansfer function looks linear but shifted

While the input signal is within the MOSFET's saturation region, it can be linearly amplified.

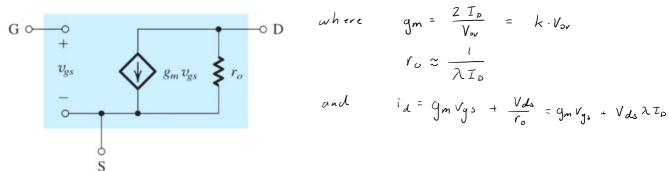

## MOSFET Bias and Small Signal Response

Thursday, February 24, 2022 5:38 PM

Det biven some MOSFET amplifier, if vgs << 2(Vos - VE) than

Small Signal Condition is satisfied.

then: ip ~ Ip + id ~ Bias Response + Signal Response

where:  $I_0 = \frac{1}{2} k (V_{GS} - V_{E})^2$  and  $i_d = k (V_{GS} - V_{E}) \cdot v_{gS}$ then the MOSFET transconductorice  $g_m = \frac{id}{V_{as}} = \frac{2 I_D}{V_{ov}} = k \cdot V_{ov}$

Det Solving for the Bias Response:

- 1) Zero all signal sources. (voltage = short, (urrent = open)

- 2) Set capacitors to open circuit. Set inductors to short circuits

- 3) Solve the circuit to find Vos. Vos. Ip, etc.

Det Solving for the Signal Response:

- 1) Zero all DC sources. (Voltage = short, Current = open)

- 2) Set the MOSFET to the following circuit: for both NMOS and PMOS

To

$$\approx \frac{2 I_p}{V_{ov}} = k \cdot V_{ov}$$

- 3) Set capacitors to short circuit. Set inductors to open circuit. Unless a frequency analysis is partormed

- 4) Solve the circuit to find Vds, Vgs, id, etc.

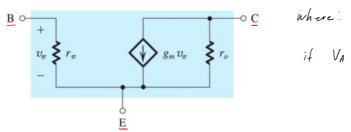

## BJT Bias and Small Signal Response

Sunday, February 27, 2022 6:14 PM

Det Liven that small signal is sutistical, are can use small signal approximation:  $\bar{L}_{c} = \bar{L}_{c} + ic : \text{ total output current is 5ias + signal}$   $g_{m} = \frac{\bar{L}_{c}}{V_{r}}$

Det Solving the bias circuit: same as MOSFET.

Zero signal sources and solve for Ic

Det Solving the signal circuit:

- 1) Zero all DC sources. (Voltage = short, Current = open)

- 2) Set the BJT to the following circuit: for both PNP and NPN

Where:  $g_m = \frac{I_c}{V_T}$ ,  $r_o = \frac{V_A}{I_c}$ ,  $r_\pi = \frac{\beta}{g_m} = \frac{V_T}{I_8}$

if  $V_A = \infty$  or  $\lambda = 0$  (ignore early effect),  $r_0 = \infty$

- 3) Set capacitors to short circuit. Set inductors to open circuit.

Unless a frequency analysis is performed

- 4) Solve the circuit to find Vds, Vgs, id. etc.

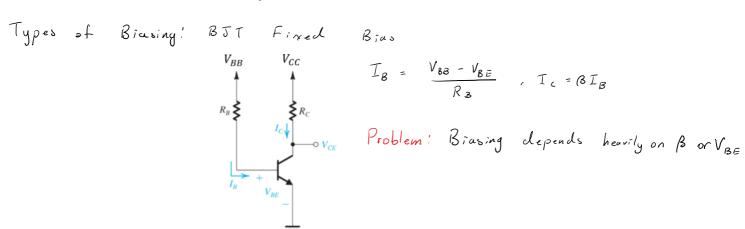

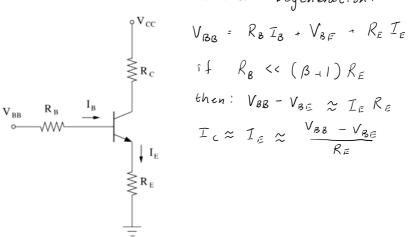

## BJT Amplifier Biasing

Tuesday, March 1, 2022 5:24 PM

Idea: for a 1357 to act as a linear amplifier, we want the 1857 to operate in the active region. Thus we want to PC bias the 1857.

$$I_{8} = \frac{V_{88} - V_{8\bar{E}}}{R_{3}}, I_{c} = 8I_{B}$$

BJT

$$V_{BB} = R_B I_B + V_{BE} + R_E I_E$$

if  $R_B << (\beta + 1) R_E$

then:  $V_{BB} - V_{BE} \approx I_E R_E$

$$I_c \approx I_{\bar{\epsilon}} \approx \frac{V_{BB} - V_{B\bar{\epsilon}}}{R_{\bar{\epsilon}}}$$

#### **MOSFET Amplifier Biasing**

Tuesday, March 1, 2022 5:38 PM

Idea: For a MOSFET to be a linear amplifier, we want it to operate in suturation.

Types of MOSFET Biasing! MOSFET Fixed Bins:  $V_{DD} V_{DS} = V_{DD} - I_{D}R_{D} \text{ and } I_{D} = 0.5 \text{ k (Vis - V_{T})}^{2}$   $R_{D}$   $V_{GS} = V_{DD} - I_{D}R_{D} \text{ and } I_{D} = 0.5 \text{ k (Vis - V_{T})}^{2}$   $V_{DS} = V_{DS} - I_{D}R_{D} \text{ and } I_{D} = 0.5 \text{ k (Vis - V_{T})}^{2}$

MOSFET Source Degeneration Bias

$V_{DS} = V_b - I_D R_S \quad and \quad I_D = 0.5 \, k \, \left( V_{bS} - V_\tau \right)^2$

# **Transistor Amplifier Configurations**

Thursday, March 3, 2022 5:01 PM

Def Transistor amplifiers

Voltage Gain of the Circuit:  $A = \frac{v_o}{v_{sig}}$

Voltage Gain of the Amplifier:  $A_v = \frac{v_o}{v_c}$

Open-loop Gain:  $A_{vo} = \frac{v_o}{v_i} \Big|_{R_L

ightarrow \infty}$

Input Resistance:  $R_i = \frac{v_i}{r}$

Output Resistance of Amplifier:  $R_o = -\frac{v_o}{i_o}\Big|_{v_i=0}$

be represented can

$v_{xy} \wedge \overline{v_i} = \overline{R_i + R_{xy}}$

as

Value of  $R_i$  is important.

- $_{\odot}~$  For  $R_{i}$  =  $R_{sig}$  ,  $v_{i}$  =  $0.5~v_{sig}$

- For  $R_i << R_{sig}$ ,  $v_i \approx 0$

2-port networks:

$A_{\rm v} = \frac{v_{\rm o}}{v_{\rm i}} = \frac{\kappa_{\rm L}}{R_{\rm L} + R_{\rm o}}$

$A_{vo}$  is the maximum possible gain of the amplifier.

Value of  $R_o$  is important.

- $_{\odot}$  For  $R_{o}$  <<  $R_{L}$  ,  $A_{v}$   $\approx$   $A_{vo}$

- $_{\odot}~{\rm For}\,R_{\rm o}$  =  $R_L$  ,  $A_v$  =  $0.5~A_{vv}$

- For  $R_o >> R_L$ ,  $A_v \approx 0$

Prefer "small"  $R_{

m p}$

a few configurations There are Det BJT amplifier for circuits

Common Collector: input applied at the base

> output taken at the emitter

Common Emitter: input applied at the

output taken at the collector

Common Base: input applied at the emitter

> output taken at the collector

Det There a few configurations for MosfET amplifier circuits:

Common in put applied Drain! atbate

> output taken at Source

input applied at Source!

output taken at Drain

Common bube! input applied at Source

output applied at Drain